PN7120 won’t not respond on the I2C bus unless CORE_RESET_CMD is sent in <1sec after power-up

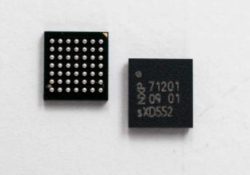

NXP’s PN7120 is NFC controller for contactless communication at 13.56MHz. It interfaces with the host CPU via the I2C bus. The I2C slave address of PN7120 is 0b010100Lx, where L is a configurable LSB of the address (by pin B2,… Continue Reading