http://www.smecy.eu/ , Funded by EU Artemis JU 100230.

My involvement: February 2011 – January 2013.

Project SMECY was the second research project I worked on, right after the Apple-CORE has ended. SMECY focused on developing tools for programming large multicore systems.

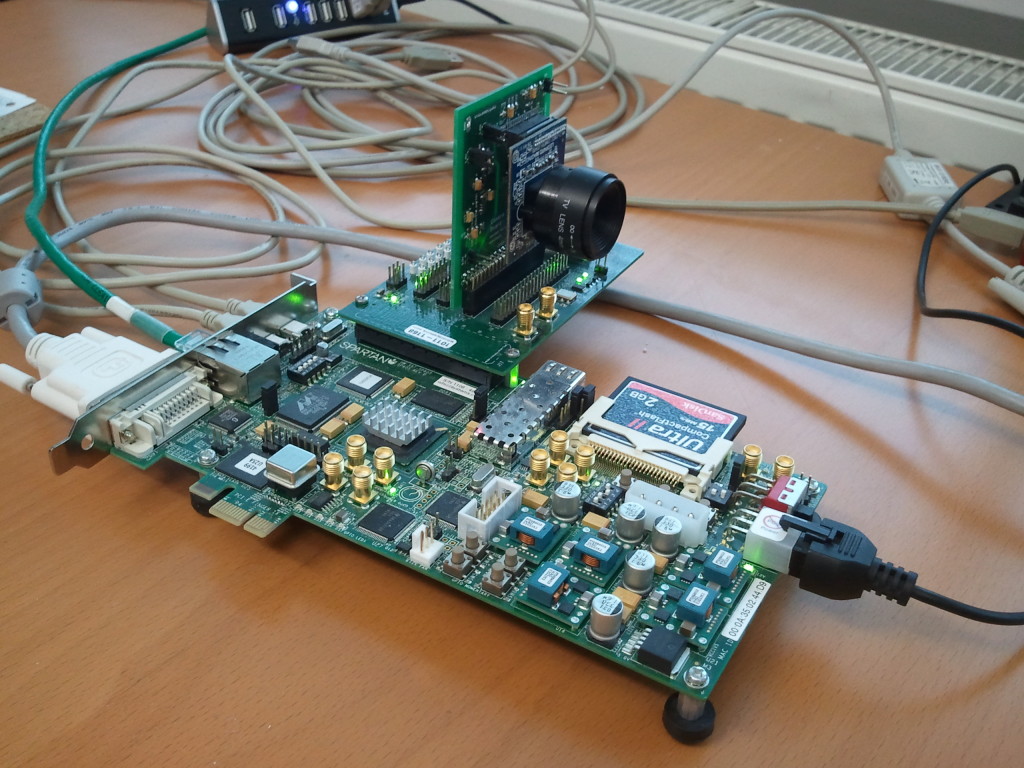

In SMECY our task in UTIA was to augment existing FPGA-based accelerator platform and make it available to project partners so that they will create parallelizing compilers from higher languages. We closely cooperated with our industrial partner CIP plus to develop a demo application: an FPGA-based board with a camera module and with an embedded system for live video motion detection.

My task in SMECY was to re-implement the accelerator platform in VHDL based on the documentation of the original version that was developed in Xilinx SystemGenerator. This resulted in two publications: characterization of the FPGA implementation results (DDECS’2012), and a method that substantially improves the performance of the platform (DSD’2012).

I also developed an optimizing C compiler for Xilinx PicoBlaze 3 soft-core 8-bit processor (micro-controller). The compiler is based on the open-source LLVM framework. The compiler was made available free of charge for non-commercial use.

Above: SP605 Spartan 6 FPGA board with camera module, as used in SMECY.